11.1 ARDIŞIL MANTIK DEVRELERİ

11.1.1 Tanım

Lojik kapı elemanlarından

oluşan ve Bölüm 8’de detaylandırılan devreler, ‘bileşik devreler’ olarak

isimlendirilir. Geri besleme ve zamanlama gibi olayların olmadığı bu devrelerde,

belli bir anda girişe gelen bilgiler belirli bir amaç doğrultusunda

işlemden geçtikten sonra çıkışa aktarılır (Şekil 11.1.a).

Devrede bellek olmaması nedeniyle, daha önceki giriş / devre

şartlarından etkilenme diye bir şey söz konusu değildir.

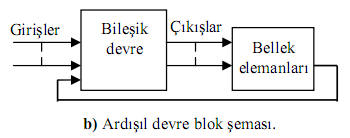

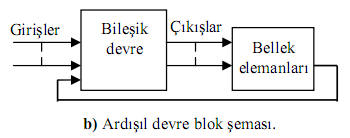

Bileşik devrelere geri besleme ve zamanlama gibi olguların eklenmesiyle oluşan devrelere, ‘sıralı veya ardışıl lojik devreler’ denir. Bileşik devre blok şeması şekil (Şekil 11.1.a)'da görülmektedir. Ardışıl devrelerde sıkça kullanılan bellek elemanları, bileşik devrelere bir geri besleme (feedback) yolu sağlayacak şekilde bağlanır (Şekil 11.1.b).

|

Şekil 11.1 Bileşik ve Ardışıl devre blok şemaları

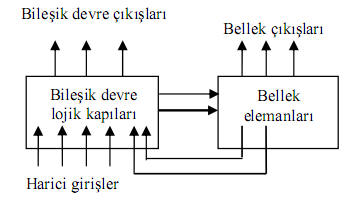

Bileşik devrenin gerçekleştirdiği işlem sonucunda, bellek elemanlarının durumunda değişiklik yapma koşulu da belirlenir. (Şekil 11.2)’deki blok şemadan görüldüğü gibi, harici girişler ve bellek elemanındaki bilgilerin değerlendirilmesi sonucu değişik çıkışlar elde edilir. Elde edilen çıkışlardan bir kısmı bellek elemanlarında saklanacak yeni ikili değeri temsil ederler. Bu işlemlerden çıkarılan sonuç; ardışıl devrenin harici çıkışlarının harici girişler ile bellek elemanlarında saklanan bilginin bir fonksiyonu olduğudur. Ardışıl (sıralı) devreler, sinyallerin zamanlamasına bağlı olarak iki grupta toplanabilir: Senkron (eş zamanlı) ve asenkron (eş zamanlı olmayan) ardışıl devreler.

|

|

Şekil 11.2 Ardışıl devrelerde önceki durumların değerlendirilmesi |

Senkron ardışıl devrelerde, bellek elemanlarını sadece belirli zaman dilimlerinde etkileyen sinyaller kullanılır. Sinyaller oluşturulurken sınırlı süreli darbeler kullanılır. Bu şekilde darbelerin kullanıldığı bir sistemde zorluk, farklı kaynaklardan aynı kapının girişlerine ulaşan iki bilginin (sinyalin) önceden tahmin edilmeyen gecikmeler göstermesi ve bilgilerin birbirinden bir miktar da olsa ayrılmasıdır. Senkron sıralı devrelerde, senkron çalışma periyodik tetikleme sinyalleri (clock pulses) dizisi üreten ana sinyal üreteci (master - clock generator) ile sağlanır. Bellek elemanlarının girişinde tetikleme sinyalleri kullanan senkron sıralı devreler, ‘tetiklemeli (saatli) sıralı devreler’ (clocked sequential logic) olarak adlandırılır. Asenkron (eş zamanlı olmayan) sıralı devrelerde, çıkışın değişmesi giriş sinyallerinin bir veya daha fazlasının değişmesine bağımlıdır. Giriş ve buna bağlı olarak çıkış durumu herhangi bir anda etkilenebilir (değişebilir). Asenkron sıralı devrelerde yaygın olarak kullanılan bellek elemanları zaman gecikmeli elemanlardır. Zaman gecikmeli bir elemanın bellek yeteneği, sinyalin eleman içinde yayılmasının belli bir zaman alması olgusundan kaynaklanmaktadır. Pratikte mantık kapılarında meydana gelen gecikme, ihtiyaç duyulan gecikmeyi sağlayarak fiziksel gecikme ünitelerine olan ihtiyacı ortadan kaldırır. Kapılarla oluşturulan asenkron devreler geri beslemeli bileşik devre olarak değerlendirilebilir ve bu şekildeki devrelerde geri besleme nedeni ile devrenin kararlı çalışma durumu bozulabilir. (Şekil 11.3)'deki seri toplayıcı devresini düşünelim. x1, x2 girişleri en az ağırlıklı basamaktan en çok ağırlıklı basamağa doğru, zamanda sıralı, iki tabanındaki iki sayıyı göstersin. Z çıkışı da bu iki tabanındaki sayıların toplamı olan sayıyı, basamak ağırlığına göre zamanda sıralı olarak göstersin. varsayalım ki x1 =12 ve x2=14 sayıları toplanacak.

|

|

Şekil 11.3 Seri Toplayıcı devresi |

(t0) ve (t4) anlarındaki girişler (00) aynı olduğu halde çıkışlar farklıdır. Benzer biçimde (t2) ve (t3) anlarındaki girişler (11) aynı olduğu halde çıkışlar farklıdır. Görülüyor ki çıkış yalnızca girişler tarafından belirlenememektedir. O halde devre bileşik değil, ardışıldır. Çıkışın belirlenebilmesi için her (ti) anında, bir evvelki (ti-1) anına ilişkin toplamın "elde" değerinin bilinmesi gerekmektedir. Bu elde'yi, makinenin herhangi bir t anındaki durumunu belirleyen bir değişken (y) olarak düşünelim. Öyle ki değişkenin (ti) anında aldığı değer (Y), ti-1 anında bu değişkenle (y), giriş değişkenlerinin aldığı değerler tarafından belirlenmiş olur. Bu noktadan çıkışla Y = f (x1,x2,y). (y) ye şimdiki durum, (Y) ye de bir sonraki durum, (y) değişkenine de durum değişkeni denir.

Örneğimiz için toplam ;

|

Tablo 11.1 Seri toplayıcıya ilişkin bağımsız değişkenler |

|

TOPLAM |

|||||

|

elde(y) |

1 |

1 |

0 |

0 |

0 |

|

x1 |

0 |

1 |

1 |

0 |

0 |

|

x2 |

0 |

1 |

1 |

1 |

0 |

|

z |

1 |

1 |

0 |

1 |

0 |

biçiminde bulunur. Artık çıkış değişkeni giriş değişkenleri ve o andaki durum

değişkeni tarafından yegane olarak belirlenmiştir.

11.1.2 Ardışıl

Makinelerin Modellendirilmesi

Ardışıl makineler matematiksel, tablo ve diyagram olmak üzere üç farklı biçimde

modellendirilebilirler. Matematiksel model (Şekil 11.3) 'de

seri girişli toplama devresi gibi, sonlu durumlu ardışıl makineleri

M = (G,Ç,D,Y,Z,D0) ile verilen bir matematiksel modelle temsil edebiliriz.

G Makinenin farklı girişlerinden oluşan

giriş kümesidir. #G = p ise girişleri temsil edebilmek için gerekli olan

giriş değişkeni sayısı n; n ≥ log2 p eşitsizliğini

sağlayan en küçük tam sayıdır. X = {x1,x2. .xn}

bağımsız giriş değişkenleri kümesi olsun.

Ç Makinenin çıkışında görülen, farklı çıkışlardan oluşan çıkış kümesidir. #Ç = g ise, çıkışları temsil edebilmek için gerekli olan çıkış değişkeni sayısı m; m ≥ log2 g eşitsizliğini sağlayan en küçük tam sayıdır.

Z = {z1,z2. ,zm} çıkış

değişkenleri kümesidir.

D Makinenin farklı durumlarından oluşan kümedir. #D = µ ise, gerekli olan durum değişkeni sayısı r, r ≥ log2 µ eşitsizliğini sağlayan en küçük tam sayıdır. y = {y1,y2. ,yr} bağımsız durum değişkenleri kümesidir.

Y = {Y1,Y2. ,Yr} bir sonraki

durum değişkenleri kümesidir. Bu küme elemanları her biri

Yit+1= Yi (xt1, xt2..., xtn, yt1, yt21,....ytr ) = Yi ( Xt, yt) : Sn+ r —> S , S = {0,1} i = 1,2,..r biçiminde tanımlanan r tane bir sonraki durum fonksiyonudur. t şimdiki anı, t+1 bir sonraki anı göstermektedir.

Z = {z1, z2,.. , zm} bağımlı çıkış değişkenleri kümesidir. Bu küme elemanlarının her biri:

Zit = Zi (xt1, xt2..., xtn, yt1, yt21,....ytr ) = Zi ( Xt, yt) : Sn+ r—> S , S = {0,1} i =1,2, ..m biçiminde tanımlanan m tane çıkış fonksiyonudur.

Zi fonksiyonları x1,...xn bağımsız giriş ve y1,. .,yr bağımsız durum değişkenlerinin fonksiyonu ise makineye "Mealy makinesi", Zi fonksiyonları yalnızca, y1,..,yr durum değişkenlerinin fonksiyonu ise makineye "Moore makinesi" denir.

Y fonksiyonlarında, fonksiyonların aldığı değer (t +1) anındaki değer; bağımsız değişkenlerin aldığı değer ise, t anındaki değerlerdir. Z fonksiyonlarında ise değişkenler ve fonksiyonların aldığı değerler aynı t anı için geçerlidir. Bundan sonra fonksiyonların t ile ilişkisi ayrıca simgelenmeyecektir.

D0 : Başlangıç durumudur. Yani bağımsız durum değişkenlerinin t0 anındaki aldıkları değerlere karşı gelen (y01,. .y02,.....y0r ) durumudur.

Örnek 11.1 Seri toplayıcı için M matematiksel modelini çıkaralım.

G giriş kümesi ve değişkenleri:

G = {G1(x1= 0, x2= 0); G2 (x1= 1, x2= 1) ; G3(x1= 1, x2= 0) ; G4 (x1= 1, x2= 1)} dir.

Ç çıkış kümesi ve değişkenleri

Ç ={(Ç1(z1= 0), Ç2(z1= 1)}dir.

D durum kümesi ve değişkenleri

D ={D1(y = 0) elde 0, D2(y = 1) elde 1} dir. (y) bağımsız durum değişkenidir.

Y bir sonraki durum ve Z çıkış fonksiyonları Tablo 11.2 ' de doğruluk tablosuyla verilen

![]() ve

ve

![]() fonksiyonlarıdır.

fonksiyonlarıdır.

|

Tablo 11.2 ' deki Seri toplayıcıya

ilişkin bağımsız değişkenler ve bir sonraki durum ve |

|

giriş(x1) |

giriş(x2) |

Durum(y) |

Y bir sonraki durum fonksiyonu |

Z çıkış fonksiyonu |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

0 |

1 |

|

0 |

1 |

0 |

0 |

1 |

|

0 |

1 |

1 |

1 |

0 |

|

1 |

0 |

0 |

0 |

1 |

|

1 |

0 |

1 |

1 |

0 |

|

1 |

1 |

0 |

1 |

0 |

|

1 |

1 |

1 |

1 |

1 |

Matematiksel olarak M = (G, Ç, D, Y, Z,,D0 ) ile verilen bir ardışıl makine, genel olarak

|

|

Şekil 11.4 Bir ardışıl makinenin en genel yapısı |

Şekil 11.4'de gösterilen devre

iki temel parçadan oluşur. Birincisi kombinezonsal parça ikincisi ise

bellek parçasıdır. Kombinezonsal parçanın girişleri, sistemin giriş değişkenleri

(x1x2. .xn) ile bağımsız

durum değişkenleri (y1y2. .yr)

dir. Kombinezonsal parçanın çıkışları da makinenin

çıkış değişkenleri (z1z2...zm) ile

bellek elemanlarının giriş fonksiyonlarıdır. Bellek elemanlarının çıkışları olan iletkenlerde, zaman

ekseninde önce (y) bağımsız değişkenlerinin sonra bağımlı bir

sonraki durum değişkenlerinin aldığı değerler gözlenir. Ard arda gelen iki

girişten, ikincisine ilişkin şimdiki durum, birinci girişe

ilişkin bir sonraki durumdur. Seri toplayıcı örneğinde (t0) anındaki

girişler için olan bir sonraki durum (0); .( t1 ) anındaki girişler

için şimdiki durumdur. Benzer biçimde (t2 ) anındaki şimdiki durum

(0); bir sonraki durum (elde) ise (1) dir. Bu yeni elde (t3) anındaki

girişler için şimdiki durumdur. Bellek elemanları bundan sonraki alt bölümde detaylı olarak

incelenecektir. Matematiksel olarak temsil edilen ardışıl makine, durum

diyagramları veya durum tablolarıyla da temsil edilebilir. Durum tablosu (Geçiş

tablosu, transition table diye de adlandırılır) satırlarında durumların (D kümesinin elemanlarının);

sütunlarında ise girişlerin (G kümesinin elemanlarının) bulunduğu bir matristir. (i). satır ve

(j) sütunun kesiştiği yerde; makinenin i. satıra

ilişkin durumunda (Di), j.sütuna ilişkin giriş (Gj)

geldiğinde ki bir sonraki durum (Dk) ile o andaki çıkış durumları (Çk)

yazılıdır (Tablo 11.3.a). Özel olarak örnek 11.1 'deki seri toplayıcı için durum

tablosu Tablo 11.3.b de verilmiştir. Bu tabloda girişler ve durumlar ilgili

değişkenler cinsinden ifade edilmiştir.

Tablo 11.3 Ardışıl makineye ilişkin durum tablosu

|

(a) Bir ardışıl makineye ilişkin genel durum tablosu |

|

G1 |

G2 |

Gj |

Gp |

|||

|

D1 |

||||||

|

D2 |

||||||

|

Dİ |

Dk,Çk |

|||||

|

Dµ |

|

(b) Seri toplayıcıya ilişkin durum tablosu |

|

X1X2 |

X1X2 |

X1X2 |

X1X2 |

|

|

00 |

01 |

11 |

10 |

|

|

giriş |

giriş |

giriş |

giriş |

|

|

Y=0 şimdiki durum |

Y,Z 0,0 |

Y,Z 0,1 |

Y,Z 1,0 |

Y,Z 0,1 |

|

Y=0 şimdiki durum |

Y,Z 0,1 |

Y,Z 1,0 |

Y,Z 1,1 |

Y,Z 1,0 |

Durum diyagramı, düğümler ve topolojik

elemanlardan oluşmuş bir diyagramdır. Düğümler durumlara karşılık gelir. Makine (Di) durumunda

(Gi) girişi altında iken bir sonraki

(Dj) durumuna geçer. Bu haldeyken eğer çıkış (zm)

olursa, (Di) düğümünden (Dj) düğümüne geçişi gösteren bir topolojik

eleman çizilir ve üzerine Gi / zm yazılır. Şekil 11.5.a' da

izah edilen bu durum diyagramının tipik bir parçası

gösterilmiştir. Örnek 11.1' deki seri toplayıcı için ilgili durum diyagramı Şekil

11.5.b' de gösterildiği gibidir. Girişler ve durumlar ilgili değişkenler

cinsinden verilmiştir.

|

|

|

b) Toplayıcıya ilişkin durum diyagramı |

|

Şekil 11.5 Durum diyagramı |

11.1.3 Ardışıl Makinelerin

Sınıflandırılması

Ardışıl makineler senkron (saatli) ve asenkron (saatsiz) makineler olmak üzere

iki ana sınıfa toplanırlar. Senkron makinelerde

periyodik saat darbeleri üreten bir merkezi saat (master - clock

generator) vardır. Bütün bellek elemanlarının saat girişlerine, bu merkezi saat

çıkışı bağlanmıştır (bakınız Şekil 11.4).

Asenkron makinelerde saat darbeleri yoktur. Temel modda (fundemental mode) ve darbe modunda (pulse mode) çalışanlar olmak üzere iki farklı türden olabilirler. Temel modda çalışan asenkron makinelerde girişler seviye biçimindedir, yani yeni bir giriş gelene kadar eski girişler durarak sistemin kararlı (stabil) bir duruma gelmesini sağlar. Yarış problemi (race condition) olmaması için birden fazla giriş değişkeni aynı anda değişmez. Darbe modunda çalışan makinelere gelince, girişleri darbe biçimindedir. Herhangi bir anda giriş değişkenlerinden yalnız biri 1 olur, diğerleri 0 olmak zorundadır. Farklı girişler arasında bütün girişler birlikte "0" olmak zorundadırlar. Şekil 11.6 ' da ardışıl makinelerin sınıflandırılması gösterilmiştir.

|

Şekil 11.6 Ardışıl makinelerin sınıflandırılması.

11.1.3.1 Bellek Elemanları

Ardışıl devrede her bir durum değişkenine ilişkin bir bellek (flip flop) elemanı

vardır. Bundan dolayı bellek elemanları 1 bitlik bir bilginin saklanmasını

sağlarlar. Çıkış şimdiki durum değişkeni y ve aynı zamanda bir sonraki durum

fonksiyonu olan Y'dir. Ayrıca durum değişkenin veya bir sonraki durum

değişkeninin tümleyeni de çıkış olarak vardır. Şimdi belli başlı bellek

elemanlarını teker teker inceleyelim.

SR bellek elemanı: iki girişli S(set), R(reset) ve iki çıkışlıdır (y,y' ) y' f

devrenin yapısı dolayısıyla doğrudan elde edildiğinden, ikinci bir çıkış

değerlendirilmiştir. Bütün diğer bellek elemanlarında da durum aynıdır, yani y

ve y' çıkışları vardır. SR bellek elemanın tanımı bir sonraki durum fonksiyonu,

durum tablosu ve durum diyagramı olarak (şekil 11.7)'de verilmiştir. (11) girişinin

hiçbir zaman uygulanmayacağı varsayılarak çıkışlar k=keyfi olarak alınmıştır. SR

bellek elemanının çalışması, girişler birbirinin zıttı iken S' nin dediğini

yapıyor biçiminde de yorumlanabilir.

Şekil 11.7 SR bellek elemanı

Şimdi (Şekil 11.8)'de verilen devreyi analiz ederek, (Şekil 11.7)'de tanımlanan SR flip flop'una karşılık geldğini gösterelim. (Şekil 11.8)'deki devrenin çıkışlarını, başlangıçta sanki biri diğerinin tümleyeni değilmiş gibi düşünüp, sonra bu çıkışların birbirlerinin tümleyeni olduklarını gözlemleyelim

a) TÜVEYA kapılarıyla gerçekleştirilen SR flip flop'u

b) Devrenin en genel durumda analizi

c) Devrenin girişlerine 11 gelmeyeceği koşulu altında sadeleşmiş doğruluk tablosu

d) Sonuçta varılan doğruluk tablosu

Şekil 11.8 SR belek elemanın devresi

(Şekil 11.8 b)'deki tabloda devrenin girişine hiçbir zaman SR (11) uygulanmayacağı düşünülürse TV'nin hiçbir zaman TV(00) durumuna gelmeyeceği görülür. Bu varsayım altında, tablodaki ilk dört satır silinebilir. Diğer taraftan TV sütunlarında 11 durumu hiç görünmemektedir. O nedenle TV(11) e karşı gelen, tablodaki ikinci dörtlü satır da silinebilir. Girişine hiçbir zaman 11 gelmeme koşulu altında basitleştirilmiş tablo (Şekil 11.8 c)'de verilmiştir. Bu tabloda ki çıkışların her biri biri diğerinin tümleyenidir. O halde V=T'dir. Şekil (11.8 d)'de varılan sonuç tablo, SR flip flop'unun tanım bağıntısına denktir.SR belek elemanının çalışması, girişler birbirinin zıttı iken S nin dediğini yapıyor biçiminde de yorumlanabilir. TÜVEYA kaplarıyla gerçekleştirilen devreye benzer TÜVE kapılarıyla gerçekleştirilen bir devre (Şekil.11.9)'de verilmiştir. TÜVEYA' lı devredekine benzer bir analizle, şekilde görülen doğruluk tablosuna varılır. Yalnızca TÜVEYA'lı devredeki 11 girişinin özelliği TÜVE li devrede 00 girişi altında oluşur ve S ile R yer değiştirmiş gibi görülür. Bu elemanı S*R* ile gösterelim. S*R* bellek elemanının çalışması, girişler birbirinin zıttı iken R nin dediğini yapıyor' biçiminde de yorumlanabilir. TÜVE' li devre ilerde tanımlayacağımız gecikme (Delay) bellek elemanın gerçekleştirilmesinde kullanılacaktır. (Şekil 11.9) ve (Şekil 11.10) de verilen devrelere temel bellek elemanları denir.

Şekil 11.9 TÜVE kapılarıyla gerçekleştirilen bir temel bellek

elemanı

Saatli SR bellek elemanı: Yukarıda tanıttığımız SR bellek elemanı asenkron makinelerde kullanılır. Saatli (Senkron) makinelerde ise saatli bellek elemanları kullanılır.Şimdi saatli SR bellek elemanını inceleyelim. SR girişlerini birer uçları saat darbesine bağlı VE kapılarından geçirdiğimizde, Şekil 6.8 görülen ve tanım tablosu verilen, saatli SR bellek elemanını elde ederiz. Saat girişi 0 olduğunda VE kapılarının çıkışları 0 olacak ve bellek elemanı bulunduğu durumunu koruyacaktır. Saat girişi 1 olduğunda ise SR girişleri VE kapılarının çıkışlarına aktarılır. Bellek elemanı girişlerin ve durumun aldığı değerlere bağlı olarak çalışır.

Şekil 11.10 Saatli SR bellek elemanı devresi, grafik gösterimi ve tanım tablosu

Tanım fonksiyonundaki y, saatten önceki şimdiki durumu; Y ise saatten sonraki

bir sonraki durumu göstermektedir. O nedenle tanım fonksiyonunda t değişken

olarak görülmemektedir. Tanım fonksiyonun ifadesi SR=11 girişlerinin hiçbir

zaman uygulanmayacağı varsayımıyla bulunmuştur. SR=0 bağıntısı bu koşulu ifade

etmektedir. Pratikte saatli SR bellek elemanı nadiren üretilir, ilerde

göreceğimiz saatli D ve JK bellek elemanları daha yaygın bir biçimde

üretilmektedir. Saatli Gecikme D ( delay) bellek elemanı: TÜVE kapılarıyla daha

önce oluşturduğumuz devreyi temel alarak (Şekil 11.11)'de oluşturulan devre, D bellek

elemanıdır. Girişine gelen işareti, iki saat darbesi aralığında çıkışında tutar.

Bir başka deyişle giriş geciktirilerek, çıkışta tutulur. Birinci saat darbesinden

sonra gelen girişler çıkışa etkili olmaz. Saat darbesi yokken (0) geri beslemeli

TÜVE kapılarının girişleri 11 olup durum değişmez, yani bellek elemanı çalışmaz.

Saat darbesi varken (1) D = 1 ise çıkış da 1, D= 0 ise çıkış 0 olur.( Şekil 11.11)'de Gecikme bellek elemanın devresi tanım tablosu (bir sonraki durum fonksiyonu)

ve durum diyagramı verilmiştir

.

Şekil.11.11 Gecikme bellek elemanı devresi, grafik gösterilimi,

tanım tablosu ve durum diyagramı

Saatli JK bellek elemanı: SR bellek elemanı gibidir; yalnızca JK=11girişi altında belirsizlik olmayıp, şimdiki durum zıddına dönüşür. Şekil 11.12 da devresi tanım tablosu,grafik gösterimi, ve durum diyagramı verilmiştir. Görüldüğü gibi TÜVEYA kapılarının çıkışları 11, biri diğerinin tümleyeni, olamayacağı için TÜVEYA kapılarının girişleri de hiçbir zaman 11 olmayacaktır, yani SR de görülen belirsizlik burada görülmeyecektir.

Şekil 11.12 JK bellek elemanı devresi, tanım tablosu, grafik gösterilimi, durum diyagramı

Saatli T tetikleme bellek elemanı Tek girişli bir bellek elamanıdır.

Girişine 0 geldiğinde durumunu korur, 1 geldiğinde ise durumunu zıddına

dönüştürür (togling). Bu elemana ilişkin bilgiler (Şekil 11.13)'de verilmiştir.

Şekil 11.13 T tetikleme bellek elemanı devresi ,tanım tablosu, grafik gösterimi ve durum diyagramı

11.1.4 Bileşik Mantık Devreleri ile Ardışıl Devrelerin Karşılaştırılması

Aşağıdaki tabloda bileşik mantık devreleri ile ardışıl mantık devereleri arasındaki belli başlı farklılıklar listelenmektedir.

Tablo 11.4 Bileşik ve Ardışıl Devreler Arasındaki Başlıca Farklar