|

|

Şekil 11.27 Dört bitlik basit bir yazmaç devresi |

11.4 SENKRON VE ASENKRON ARDIŞIL DEVRE TASARIMI

11.4.1 Tanım

Yazmaçlar, her biri birer bitlik bilgi tutan bellek elemanları ile bilginin

işlenmesini denetleyen kapı elemanlarından oluşur. Sayıcılar ard arda gelen saat

darbeleriyle daha önce belirlenmiş durumlara sırasıyla geçen ardışıl

devrelerdir. Sayıcıları, kapı elemanlarıyla durum geçişleri sağlanan bir yazmaç

gibi düşünmek mümkündür. Buna rağmen sayıcılar ayrı bir grup olarak

incelenecektir.

Rastgele erişimli bellekler, RAM (Random Access Memory)'ler, hem bellekteki bilginin okunmasını (read) hem de belleğe bir bilginin yazılmasını (write) sağlarlar. Bunlara okuyan ve yazan bellek elemanları da (read-write memory) denir. Burada sözünü edeceğimiz bellek elemanları bilgisayar tasarımında ve ardışıl devre tasarımında yaygın bir biçimde kullanılırlar.

Şekil 11.27 Dört bitlik basit bir yazmaç devresi

11.4.2 Yazmaçlar

En basit bir yazmaç devresi Şekil 11.27'de görüldüğü gibi yalnızca dört D tipi

bellek elemanlarından oluşur. Saat girişi geldiğinde girişteki dört bitlik bir

bilgi belleğe yazılmış olur ve bir sonraki saat darbesi gelene kadar bu bilgi

saklanır. Yazmaçlarda kullanılan bellek elemanları genellikle kenar

tetiklemelidirler.

Lojik sistemlerde sistemin bir ana saati (master clock) vardır ve bütün bellek elemanlarının saat girişine bağlıdır. Oysa bazen belli bellek elemanlarının belli zamanlarda çalıştırılması gereksinimi doğar. Bu nedenle ayrı bir kontrol girişi (load) kullanılır. Şekil 11.28'de load girişli, RS bellek elemanlı, dört bitlik bir paralel yüklemeli yazmacın lojik devresi verilmiştir.

Load girişi saat darbe girişi ile VE lendirilip bellek elemanlarının saat girişlerine bağlanabilirdi. Lojik sistemlerde saat girişlerinin doğrudan bellek girişlerine bağlanması uygundur, çünkü aksi halde alt sistemlerin birbiriyle senkron çalışamama sorunu çıkabilir. Load girişindeki, tümleyen almayan girişi, çıkışı ile aynı olan (noninverting buffer) kapı, çıkış yelpazesini (fanout) arttırmak içindir. Yani bu kapı 8 VE kapısının girişine yeterli akımı sağlar.

|

|

Şekil 11.28 Paralel yüklemeli RS bellek elemanlı yazmacının lojik devresi |

Şekil 11.28'de paralel yüklemeli RS bellek elemanlı bir yazmaçın lojik devresi gşsterilmektedir. Bu devrede Clear girişi, load girişi gibi, bir buffer kapısından bellek elemanlarının girişine bağlanmıştır. Giriş (0)olduğunda (bellek elemanlarının girişinde ki küçük yuvarlak bunu göstermek içindir) yazmaçta (0000) bilgisi oluşur. Saat girişi bir tümleyen elemanı üzerinden bellek elemanlarına bağlanmıştır. Tümleyen elemanı, hem gerekli çıkış yelpazesini (fanout) arttırır hem de saat darbesinin düşen kenarında tetiklemeyi sağlar. Şimdi Tablo 11.9 'de doğruluk tablosu verilen paralel yüklemeli yazmacın çalışmasını inceleyelim.

|

Tablo 11.9 Paralel yüklemeli yazmacının doğruluk tablosu |

|

Clear |

Load |

Saat |

I1 |

I2 |

I3 |

I4 |

Y1 |

Y2 |

Y3 |

Y4 |

|

0 |

x |

x |

x |

x |

x |

x |

0 |

0 |

0 |

0 |

|

1 |

0 |

x |

x |

x |

x |

x |

y1 |

y2 |

y3 |

y4 |

|

1 |

1 |

↓ |

I1 |

I2 |

I3 |

I4 |

I1 |

I2 |

I3 |

I4 |

Clear girişi, diğer bütün girişlerden bağımsız olarak, çıkışı

sıfırlamaktadır. Clear (1) ve load (0) iken çıkış durumu korunmaktadır. Bu

işlem bütün VE kapılarının çıkışlarını dolayısıyla SR bellek elemanlarının

girişlerini (00) yapar, SR bellek elemanı tanımı uyarınca da saat darbesi gelse

bile çıkışlar değişmez. Clear ve Load (1) iken saat darbesinin düşen

kenarında ise paralel yükleme işlemi hasıl olur. Bütün bellek elemanlarının girişleri

Si = Ii ve Ri = Ii şeklindedir. SR

bellek elemanı tanımı gereğince çıkışlar Si = Ii

olur.

Yukarıda incelediğimiz paralel yüklemeli yazmaç SR bellek elemanlarıyla gerçekleştirilmiştir, diğer bellek elemanlarıyla da paralel yüklemeli yazmaç gerçekleştirmek mümkündür. Çeşitli firmaların kataloglarında paralel yüklemeli yazmaçların hem lojik devreleri hem de doğruluk tabloları verilmiştir.

11.4.2.2 Paralel yüklemeli

yazmaçlarla ardışıl devre tasarımı

Paralel yüklemeli yazmaçların iyi bir uygulaması ardışıl devre sentezidir. Daha

önce gördüğümüz gibi ardışıl devreler bellek ve kombinezonsal olmak üzere iki

parçadan oluşuyordu. Bellek parçası yerine yazmaçlar kullanarak da sentez Şekil

11.28 'de görüldüğü gibi yapılabilir.

Kombinezonsal kısım, kapı elemanlarından oluşturulabileceği gibi ROM ' lar ile de gerçekleştirilebilir. Yazmacın çıkışları, saat darbesi öncesi için şimdiki durum değişkenlerine; saat darbesi sonrası için bir sonraki durum değişkenlerine karşı gelir ve kombinezonsal devre girişine bağlanmıştır. Diğer girişler ise ardışıl devrenin bağımsız girişleridir. Kombinezonsal devrenin bir kısım çıkışları, bağımlı bir sonraki durum değişkenlerine karşı gelmektedir ve bir geri besleme ile yazmacın girişlerine bağlanmıştır. Diğer çıkışlar ardışıl devrenin çıkışlarıdır. Bir MSI yazmaç devresinde 4 bellek elemanı olduğunu düşünürsek, böyle bir yazmaç ile 16 durumlu bir ardışıl devre gerçeklenebilir.

|

|

Şekil 11.29 Paralel yüklemeli yazmaçlı ardışıl devrenin genel yapısı |

|

|

Şekil 11.30 Dizi detektörünün paralel yüklemeli yazmaç ile gerçekleştirilmesi |

11.4.2.3 Ötelemeli yazmaçlar

İçerisindeki bilgiyi her saat darbesi geldiğinde, bir bit öteye kaydıran ve seri

girişinden de bir bitlik bilgiyi içine alabilen yazmaçlara ötelemeli yazmaçlar

denir. En basit bir ötelemeli yazmaç, çıkışları girişlerine kaskad bağlı D tipi

bellek elemanlarından oluşur (Şekil 11.31). Bu devrede her bir saat darbesi

geldiğinde bilgi soldan sağa doğru ötelenir.

Yazmacın saat darbelerini kontrol eden ikinci bir giriş, load girişi, kullanılabilir. Bunun için saat darbeleri ile load girişi VE elemanı üzerinden saat girişine bağlanır. Load girişi yazmacın bit kapasitesi kadar bir zaman aralığında çalışmasını sağlar. Seri bilgi kelime (word) denilen ard arda bit gruplarından oluşur. Kelimeler 4, 8, 16, 32 bit uzunluklarında olabilirler.

Örneğin dört bitlik bir kelime uzunluğu olan yazmacın kapasitesi dört bit yani bir kelimedir. Her seferinde bir kelimelik bilginin ötelenmesi isteniyorsa load girişinin 1 olma uzunluğu, kelime zamanı (word time) dört saat darbesini kapsayacak kadar olmalıdır (Şekil 11.32).

|

Şekil 11.31 Ötelemeli kaydedici |

|

|

|

Şekil 11.32 Ötelemeli kaydedici |

Bir kelime zamanında saat darbeleri ve giriş çıkışlarda gözlenen işaretler Şekil 11.32'de verilmiştir. Bilgisayarlarda bilgi seri, Paralel veya ikisinin de olduğu biçimlerde işlenebilir. Seri işlemede her bir saat darbesiyle bir bit işlenirken, paralel işlemede her bir saat darbesiyle bir kelimelik bilgi işlenir. Genellikle bilgisayarlarda paralel işleme söz konusudur. Uzağa bilginin gönderilmesinde ise bilgi, transmisyon ortamının maliyetini azaltmak için, genellikle seri gönderilir.

11.4.2.4 Çift yönlü seri ve

paralel yüklemeli ötelemeli kaydediciler

Bundan önce söz ettiğimiz yazmaçlarda bütün kontrol girişleri birlikte yoktu.

Şimdi inceleyeceğimiz de ise sağa, sola öteleme ve paralel yükleme kontrol

girişleri olacak. Yazmaçlar, sağa sola kaydırma ve paralel yükleme kontrol

girişleriyle çok amaçlı olarak kullanılabilirler. Örneğin verinin seriden

paralele veya paralelden seriye dönüştürülmesi mümkündür. Şekil 11.33'te dört

farklı çalışma modu olan 741114 tipi bir yazmacın lojik devresi verilmiştir.

|

|

Şekil 11.33 Kaydırmalı ve paralel yüklemeli yazmaç lojik devresi |

Yazmacın s0, s1 girişleriyle kontrol

edilen dört çalışma modu vardır:

s0 s1 = 00 ise çıkışta hiçbir değişiklik olmaz,

s0 s1 = 01 ise çıkış sağa ötelenir ve sağa öteleme

girişindeki bit A4'te görülürken A1'deki bit kaybolur,

s0 s1 = 10 ise çıkış sola ötelenir ve sola öteleme girişindeki bit A1'de görülürken A4'teki bit kaybolur,

s0 s1 = 11 ise paralel girişler çıkışta görülür.

Bu dört çalışma modunu 4X1 'lik MUX 'ların kontrol

girişleriyle sağlamak mümkündür. MUX 'ların 0 girişleri bağlı oldukları bellek

elemanlarının girişlerine bağlıdır, yani 00 modunda çıkışlar değişmez. MUX 'ların

1 girişlerine bir soldaki bellek elemanlarının çıkışları, sağa ötelemeyi

sağlamak üzere bağlanmıştır. MUX 'ların 2 girişlerine ise bir sağdaki bellek

elemanlarının çıkışları, sola ötelemeyi sağlamak için bağlanmıştır. Nihayet MUX

'ların 3 girişlerine paralel girişler bağlanmıştır, öyle ki saat darbesi

geldiğinde bu paralel girişler çıkışta görülürler.

Böyle bir yazmaçta seri girişlere gelecek 4 bitlik kelimeler dört saat

darbesiyle çıkışta paralel olarak görülürler veya çıkıştaki 4 bitlik paralel

veri üç saat darbesiyle A1 veya A4'ten seri olarak alınabilir. Bir uygulama

olarak yazmaçları, daha önce gördüğümüz seri toplayıcının giriş ve çıkış

verisini toplamada kullanalım.

Toplanacak sayılar dört kelime uzunluklu olsun ve birer yazmaçta tutulsunlar. A ve B yazmaçlarına toplanacak sayılar paralel girilebilir. Çıkıştaki toplam sayıyı da kullandığımız A yazmacına seri olarak kaydedelim. Bu durumda çıkışın yazıldığı A yazmacının, üzerindeki toplanacak sayı silinmiş olur. Bu, şekil 11.34' teki lojik devrede verilmiştir.

|

|

Şekil 11.34 Kaydedicili seri toplayıcı |

Paralel yükleme modunda toplayacağımız dört bitlik A ve B sayılarının A ve B yazmaçlarına yüklediğimizi varsayalım. SR bellek elemanının başlangıç durumu (0) olsun. A ve B sayılarının en az ağırlıklı bitlerinin toplamı (z) çıkışında ve dolayısıyla A yazmacının seri girişinde görülecektir.

Yazmaçlar öteleme modunda iken, saat darbesi geldiğinde, en az ağırlıklı bitlerin toplamı A yazmacının en sol bitine girer. A ve B sayılarının ikinci ağırlıklı bitleri ise seri toplayıcının girişlerine gelir. En az ağırlıklı bitlerden gelen elde ise SR bellek elemanının çıkışı y'de olacaktır. Böylece z çıkışı, ikinci bitler ile birinci bitlerin eldesinin toplamı olur ve A yazmacının seri girişine gelir.

Bu işlem dört saat darbesi boyunca devam ettiğinde A ve B sayılarının toplamı A yazmacında görülür. Bu arada B yazmacına üçüncü bir sayı girilmiş olsun. Bu halde A + B 'nin üçüncü sayı ile toplamı, yeni bir dört saat darbelik sürede, A yazmacında elde edilebilir.

11.4.3 Frekans Bölücüler ve

Tasarımı

Yukarı ve aşağı sayıcıların zaman diyagramlarına baktığımız zaman her FF'nin

giriş sinyal frekansını 2'ye bölme özelliği gösterdiğini görebiliriz.CP 16 hz

ise FF1' in Q çıkışındaki frekansı 8 hz, FF2'nin Q

çıkışındaki frekansı 4 hz ,FF3'ün Q çıkışındaki frekansı 2 hz, FF4'ün

Q çıkışındaki frekans ise 1 hz dir. Genel olarak n bitlik bir binary sayıcının

çıkış frekansı;

Fout = Fclock/2n formülü ile elde edilir.

Aşağıdaki sayıcı devresinde görülen her bir flip-flop'un girişine gelen sinyalin frekansı 2'ye bölündüğünden bu sayıcı devresi frekans bölücü devre özelliği gösterir.

|

11.35 4 bitlik asenkron aşağı sayıcı devresi |

11.4.4 Örnek Ardışıl Devre Tasarımları

Örnek 1: Eş zamanlı (Senkron) Ardışıl Devre Tasarım Örneği

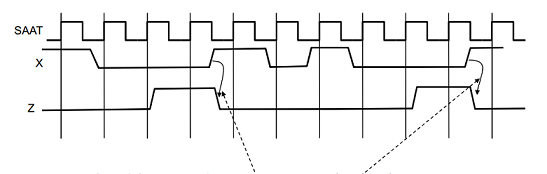

Bir girişi (X) ve bir çıkışı (Z) olan eşzamanlı ardışıl bir devre tasarlanacaktır. Devrenin girişi birbirini izleyen en az iki saat darbesi boyunca lojik 0'da kaldıktan sonra, girişten lojik 0 geldiği sürece devrenin çıkışı lojik 1 olacaktır. Problemi daha iyi anlayabilmek için aşağıdaki zamanlama diyagramı incelenebilir.

11.36 Zamanlama Diyagramı

Devre Tasarım için takip edilecek adımlar aşağıda izah edilmektedir:

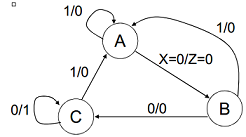

1. Durum Diyagramının Oluşturulması

Önce sözle anlatımdan (zamanlama diyagramından) durum diyagramını şekil 11.37'de görüldüğü gibi oluştururuz.

11.37

Durum Diyagramı

Yukarıdaki durum diyagramında da görüldüğü

üzere elimizde 3 durum (state vardır):

A: Hiç sıfır gelmedi

durumu

B: Birinci sıfır geldi durumu

C:

İkinci sıfır geldi durumu

2. Durum Geçiş

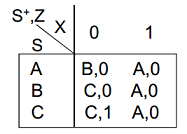

Tablosunun ve Durum Kodlarının Oluşturulması

Durum diyagramı baz

alınarak aşağıdaki durum geçiş tablosu oluşturulur.

11.38 Durum Geçiş Tablosu

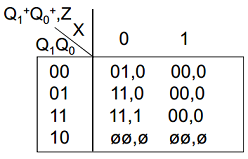

Devrenin işlevini yerine getirmesi için gerekli durum kodlamaları A: 00, B: 01, C: 11 olacak şekilde belirlenmiştir. Durum değişkenlerimiz (Flip-Floplarımız) ise Q1 ve Q0'dır. Buna göre aşağıdaki durum değişkenleri geçiş tablosu elde edilir:

11.39

Durum Değişkenleri Geçiş Tablosu

3. Durum

Değişkenlerinin Geçişlerinin Belirlenmesi

Devrenin durum geçiş tablosundan

yararlanılarak her durum değişkeninin (flip-flopun) hangi geçişi yapacağı ayrı

ayrı belirlenir.

11.40 Durum Değişkenleri Geçiş Tablosu

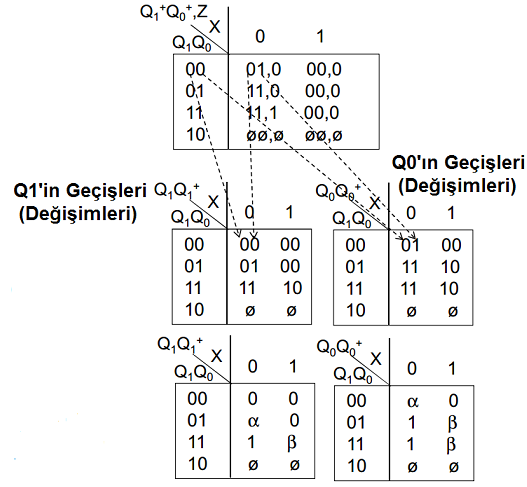

4. Kullanılacak Flip-Floplara Karar Verilmesi

Bu örnekte pozitif kenar tetiklemeli D flip-floplar kullanılacaktır. Bir önceki adımda her flip-flopun hangi geçişi yapması gerektiği belirlenmişti. Bu aşamada seçilen flip-flopa istenilen bir geçişin yaptırılabilmesi için girişlerine hangi değerlerin uygulanması gerektiği araştırılacaktır. Bunun için kullanılacak flip-flopun geçiş tablosundan yararlanılacaktır.

Aşağıdaki şekilde gösterilen D Flip-Flop'un geçiş tablosu, belli bir durum değişikliğinin D Flip-Flop'la gerçekleşmesi için girişlere uygulanması gereken değerleri gösterir. Görüldüğü gibi D flip-flop'un tablosu basittir. D girişine verilmesi gereken değer sonraki durum değişkenin değeri ile aynıdır.

11.41

D Flip-Flop'un Geçiş Tablosu

Durum geçiş tablolarına flip-flop'un alması gereken giriş değerleri yerleştirilir. İfadeleri kolaylıkla yazabilmek için bu tablolar aiağıda gösterildiği üzere karnaugh diyagramı olarak oluşturulmuştur. Böylece flip-flopları sürerek sonraki durumu belirleyen F fonksiyonuelde edilmiş olur.

11.42 D Flip-Flop'ların Durum Geçiş Tabloları

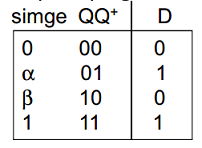

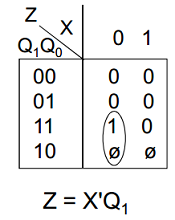

5. Çıkış Tablosu Kullanılarak Akış Fonksiyonunun Belirlenmesi

F ve G fonksiyonları, fonksiyonlar oldukça basit olduğundan indirgeme yöntemi kulanılmadan aşağıdaki karnaugh tablosunda görüldüğü gibi elde edilebilir.

11.43

Çıkış Fonksiyonunun Belirlendiği Karnaugh Haritası

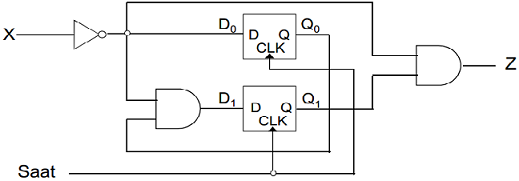

6. Devrenin Lojik Elemanlar ile Gerçeklenip Çizilmesi

11.44 Devre Şeması

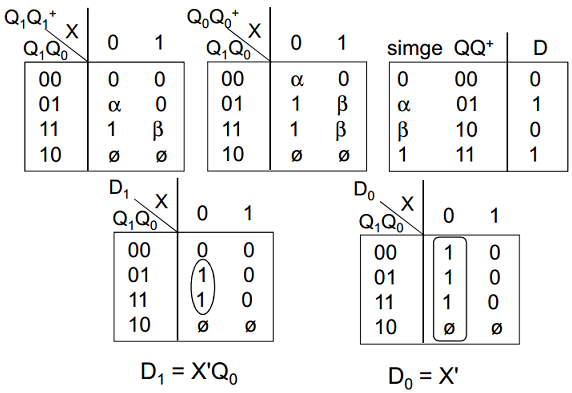

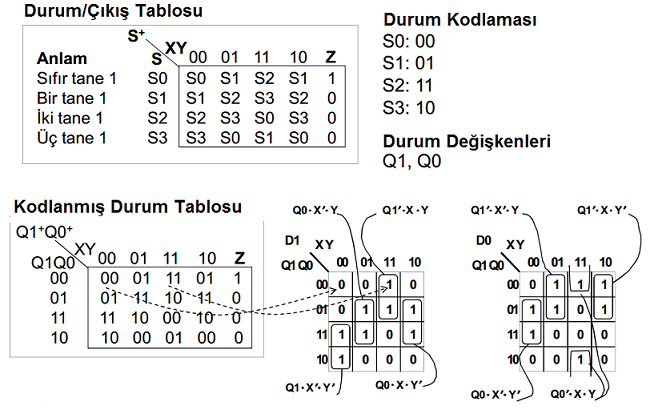

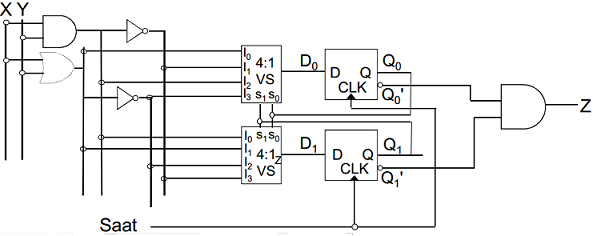

Örnek 2: İki girişi (X,Y) bir çıkışı (Z) olan senkron ardışıl bir devre tasarımı

İki girişi (X,Y) bir çıkışı (Z) olan senkron ardışıl bir devre tasarlanacaktır. Makinanın çalışmaya başlamasından itibaren girişlerden gelen '1' değerlerinin sayısı 4'ün katları ise devrenin çıkışı '1' değerini alacaktır. Aksi durumda çıkış '0' olacaktır. Girişten hiç '1' gelmemesi (0 tane) durumunda çıkışı '1' olacaktır.

Devrenin modulo 4 işlemini gerçekleştirmesi ve kalan 0 ise çıkışını '1' yapması istenmektedir. Bu makine 4 adet durum ile gerçeklenebilir:

1. Kalan 0: S0

2. Kalan 1:

S1

3. Kalan 2: S2

4. Kalan 3: S3

Durum geçiş tablosu, durum kodlaması ve ve kodlanmış

durum çıkış tablosu aşağıdaki şekilde gösterildği gibi oluşturulur.

11.45 Örnek 2 için Durum Tabloları

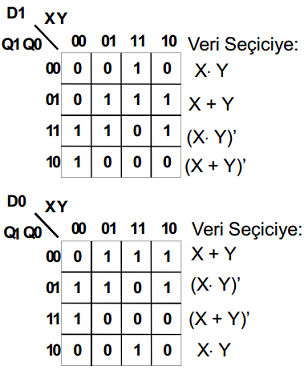

D girişlerine gelmesi gereken değerler aşağıdaki karno tablolarında özetlenmiştir:

11.46 D Girişlerine Girmesi Gereken Değerleri Gösterir Karnaugh Tabloları

11.47 Devre Şeması